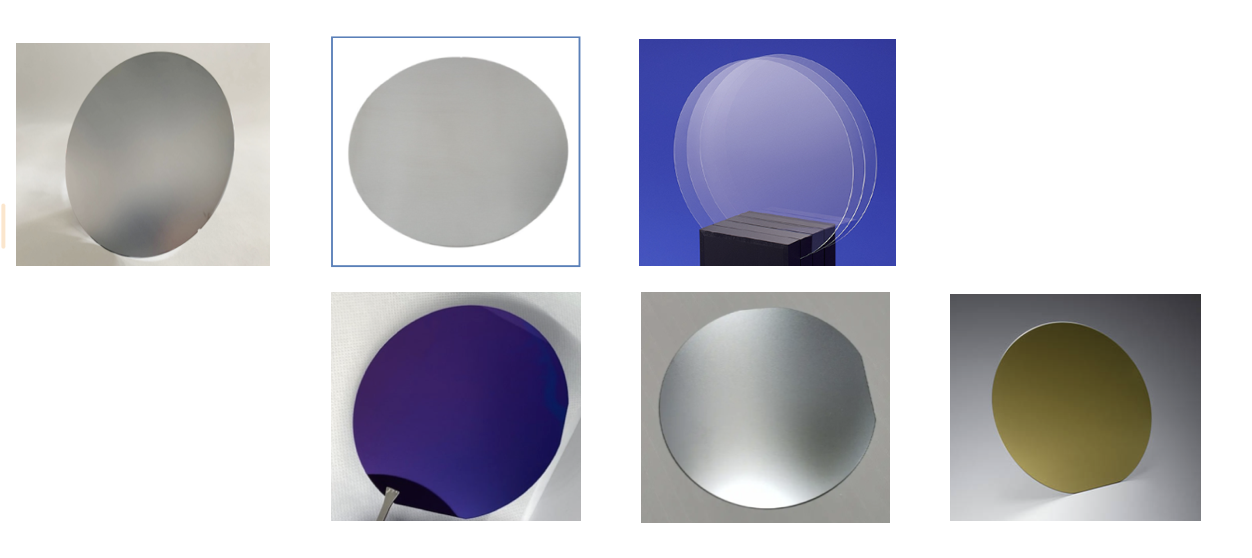

晶圓薄化Wafer Thinning

晶圓薄化(Wafer Thinning)是半導體後段製程的關鍵技術,將晶圓背面研磨至極薄,主要應用於3D封裝、功率元件(如 SiC, GaN)及晶背供電(ESPDN)技術。晶圓薄化能實現輕薄短小、降低導通電阻、降低功率元件熱能的累積,提高元件的壽命與效能,同時解決高密度堆疊空間限制。

●主要應用領域:

- 晶背供電 (Backside Power Delivery):將供電線路從晶圓正面移至背面,提升訊號傳輸效率並減少損耗。

- 功率半導體:如 MOSFET, IGBT, SiC/GaN 等,薄化可有效降低導通電阻。

- 3D 封裝 (TSV):透過矽穿孔(Through-Silicon Via)技術堆疊晶片,薄化能降穿孔深度,提高封裝產能。

我們提供高規格晶圓薄化及切割技術接受客戶來料代工,並且也有相關產品提供諮詢,多方面滿足客戶需求,歡迎來電洽詢!